# Low Drop Out regulators: basic principles and design examples

Prof Lorenzo Capineri

Rev 2 . 2015

## **Topics**

Basic theory of LDO

Analysis of technical characteristics of TPS749xx (TI) device

Design of a power supply system for an analog-digital processing board

# LDO: Low Dropout regulator

Low dropout regulators (LDOs) are linear (dissipative) regulators. They are a simple inexpensive way to regulate an output voltage that is powered from a higher voltage input. They are easy to design with and use. For most applications, the parameters in an LDO datasheet are usually very clear and easy to understand.

However, other applications require the designer to examine the datasheet more closely to determine whether or not the LDO is suitable for the specific circuit conditions.

The main advantage (and difference) from 3 or 4 terminal linear regulators with power BJT pass element is the operation with small drop out voltage within a load current limit.

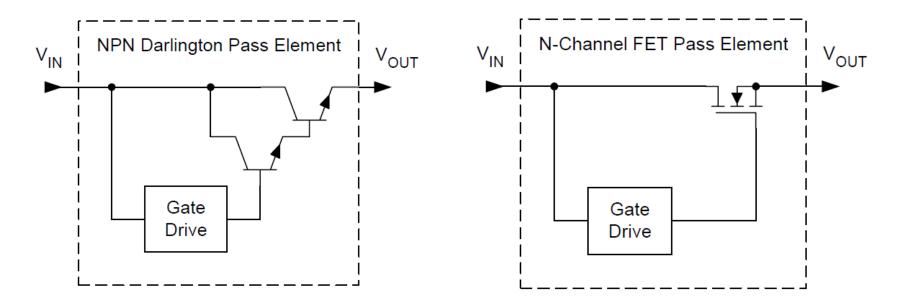

## Standard Regulators and LDOs

Darlington configuration needs to operate with high Vce in the linear region because the summation of the two VBE's.

Standard linear regulators have voltage drops as high as 2 V which are acceptable for applications with large input-to-output voltage difference such as generating 2.5 V from a 5 V input.

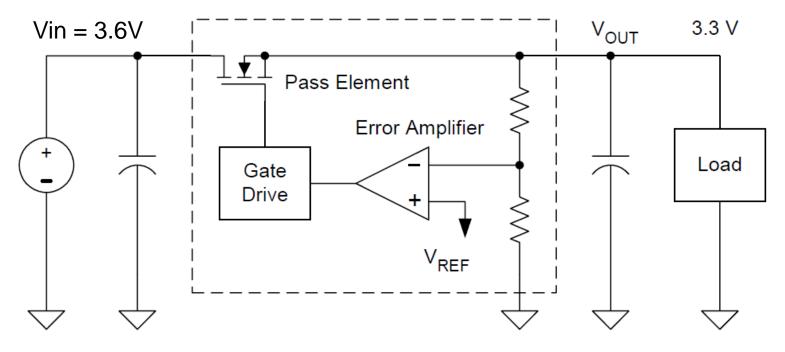

## LDO block diagram

The power Mosfet works as series pass element and regulates the output voltage by the R<sub>dsON</sub>.

Power Mosfet operating in saturation has very low value of Rdson and so the small drop out voltages → Vin close to Vout can be regulated efficiently.

Example: Vout = 3.3 V with Vin = 3.6V Li-lon battery requires the operation with only 300 mV of drop out voltage and good efficiency!!

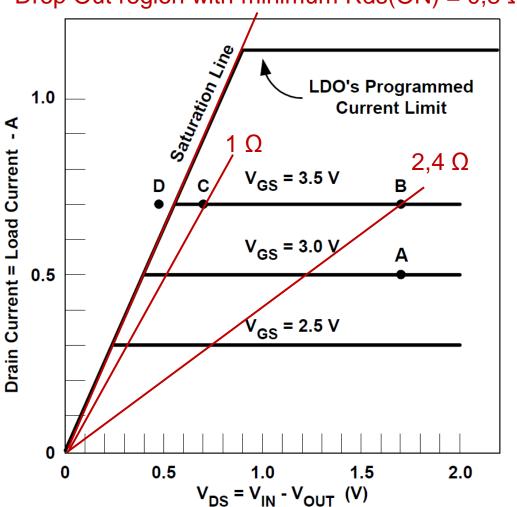

# Operating region of an LDO's N- channel pass element

Drop Out region with minimum Rds(ON) =  $0.8 \Omega$

#### Rated drop out voltage

Data sheets provide the maximum  $V_{DROPOUT}$  for a rated output current ( $I_{OUT}$ ) at nominal  $V_{OUT}$  in a specified temperature range :

$$V_{DROPOUT} = I_{OUT} \times R_{dsON}$$

- Depending on the rated output current,  $R_{dsON}$  goes from 0,1  $\Omega$  to 10  $\Omega$  and with output current from 0.1 0.5 A.

- R<sub>dsON</sub> values depends on die size and package type.

- Typically line voltage regulation coefficient are very small also for low output voltages as low as 1.2 V.

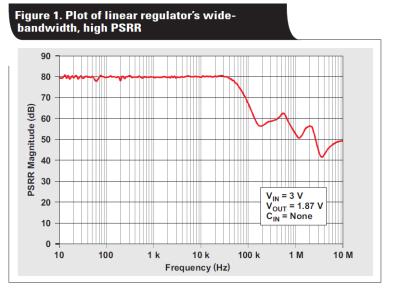

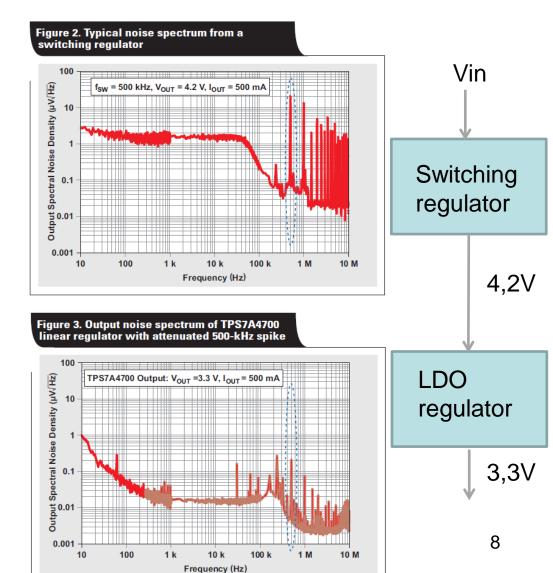

#### LDO noise

$$PSRR = 20 \times log \left( \frac{V_{IN\_ripple}}{V_{OUT\_ripple}} \right).$$

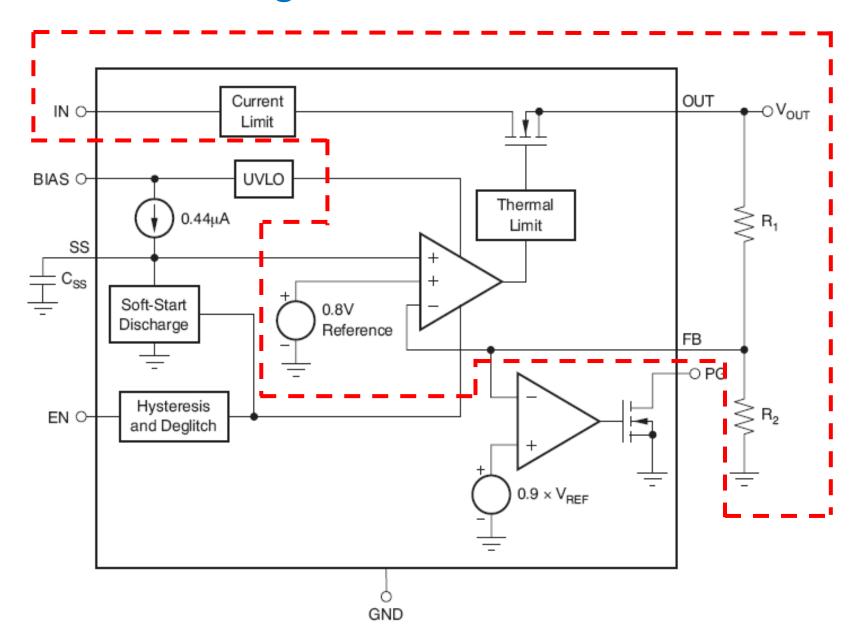

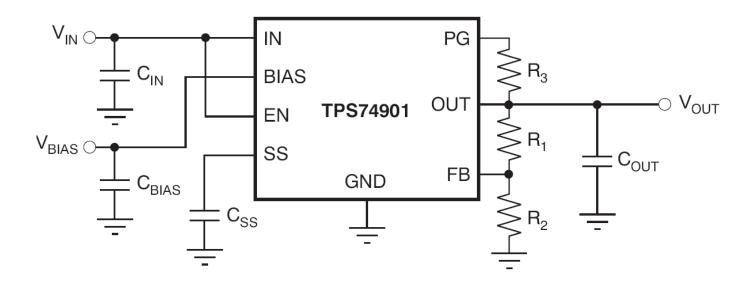

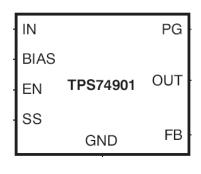

#### Block diagram of device TPS74901

#### Variable output voltage with TPS74901

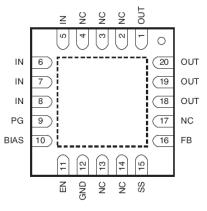

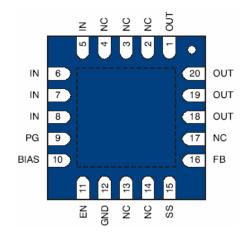

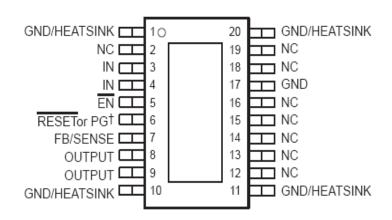

#### RGW PACKAGE QFN-20 (TOP VIEW)

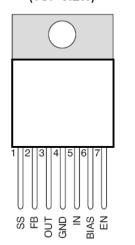

#### KTW PACKAGE DDPAK-7 (TOP VIEW)

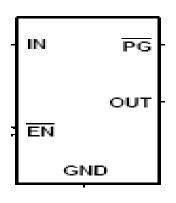

- <u>IN</u> Input voltage

- **BIAS** Reference voltage and internal circuit supply voltage.

- **EN (ENABLE)** Enable active positive

- **SS (SOFT START)** With external capacitor the start-up time can be controlled. Otherwise the default start-up time is100µs

- <u>PG (POWER GOOD)</u> Indicates when the output voltages is above a defined threshold (typivally 90% of the nominal output voltage) and the device is fully operating.

- <u>OUT</u> Regulated output voltage

- <u>FB (FEEDBACK)</u> voltage feed back input

- <u>GND</u>

- <u>NC</u>

- <u>PAD/TAB</u> Thermal PAD to be soldered to ground plane of PCB to dissipate thermal power.

#### **ELECTRICAL CHARACTERISTICS**

At  $T_J$  = -40°C to +125°C,  $V_{EN}$  = 1.1V,  $V_{IN}$  =  $V_{OUT}$  + 0.3V,  $C_{BIAS}$  = 0.1 $\mu$ F,  $C_{IN}$  =  $C_{OUT}$  = 10 $\mu$ F,  $C_{NR}$  = 1nF,  $I_{OUT}$  = 50mA, and  $V_{BIAS}$  = 5.0V, unless otherwise noted. Typical values are at  $T_J$  = +25°C.

|                                    |                                                  |                                                                                  | TPS74901                           |       |       |      |

|------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------|-------|-------|------|

|                                    | PARAMETER                                        | TEST CONDITIONS                                                                  | MIN                                | TYP   | MAX   | UNIT |

| $V_{IN}$                           | Input voltage range                              |                                                                                  | V <sub>OUT</sub> + V <sub>DO</sub> |       | 5.5   | V    |

| $V_{BIAS}$                         | Bias pin voltage range                           |                                                                                  | 2.7                                |       | 5.5   | V    |

| $V_{REF}$                          | Internal reference (Adj.)                        | T <sub>J</sub> = +25°C                                                           | 0.798                              | 0.802 | 0.806 | V    |

| V <sub>OUT</sub>                   | Output voltage range                             | V <sub>IN</sub> = 5V, I <sub>OUT</sub> = 3.0V                                    | V <sub>REF</sub>                   |       | 3.6   | V    |

|                                    | Accuracy<br>(RGW package) <sup>(1)</sup>         | $V_{OUT}$ + 2.2V $\leq$ $V_{BIAS} \leq$ 5.5V,<br>50mA $\leq$ $I_{OUT} \leq$ 3.0A | -2                                 | ±0.5  | 2     | %    |

|                                    | Accuracy<br>(KTW package) <sup>(1)</sup>         | $V_{OUT}$ + 2.4V $\leq$ $V_{BIAS} \leq$ 5.5V,<br>50mA $\leq$ $I_{OUT} \leq$ 3.0A | -2                                 | ±0.5  | 2     | %    |

| V <sub>OUT</sub> /V <sub>IN</sub>  | Line regulation                                  | $V_{OUT\ (NOM)} + 0.3 \le V_{IN} \le 5.5V$                                       |                                    | 0.03  |       | %N   |

| V <sub>OUT</sub> /I <sub>OUT</sub> | Load regulation                                  | $50\text{mA} \le I_{\text{OUT}} \le 3.0\text{A}$                                 |                                    | 0.09  |       | %/A  |

| V <sub>DO</sub>                    | V <sub>IN</sub> dropout voltage <sup>(2)</sup>   | $I_{OUT} = 3.0A,$ $V_{BIAS} - V_{OUT (NOM)} \ge 3.25V^{(3)}$                     |                                    | 120   | 280   | m∨   |

|                                    | V <sub>BIAS</sub> dropout voltage <sup>(2)</sup> | $I_{OUT} = 3.0A$ , $V_{IN} = V_{BIAS}$                                           |                                    | 1.31  | 1.75  | V    |

| I <sub>CL</sub>                    | Current limit                                    | V <sub>OUT</sub> = 80% × V <sub>OUT (NOM)</sub> , RGW<br>Package                 | 3.9                                | 4.6   | 5.5   | ^    |

|                                    |                                                  | V <sub>OUT</sub> = 80% × V <sub>OUT (NOM)</sub> , KTW<br>Package                 | 3.8                                | 4.6   | 5.5   | A    |

| I <sub>BIAS</sub>                  | Bias pin current                                 |                                                                                  |                                    | 1     | 2     | mA   |

| I <sub>SHDN</sub>    | Shutdown supply current (I <sub>GND</sub> )                     | $V_{EN} \le 0.4V$                                                                 |     | 1                     | 50   | μА                |

|----------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|-----------------------|------|-------------------|

| I <sub>FB</sub>      | Feedback pin current                                            |                                                                                   | -1  | 0.150                 | 1    | μA                |

| PSRR                 | Power-supply rejection (V <sub>IN</sub> to V <sub>OUT</sub> )   | 1kHz, I <sub>OUT</sub> = 1.5A,<br>V <sub>IN</sub> = 1.8V, V <sub>OUT</sub> = 1.5V |     | 60                    |      | - dB              |

|                      |                                                                 | 300kHz, $I_{OUT} = 1.5A$ ,<br>$V_{IN} = 1.8V$ , $V_{OUT} = 1.5V$                  |     | 30                    |      |                   |

|                      | Power-supply rejection (V <sub>BIAS</sub> to V <sub>OUT</sub> ) | 1kHz, I <sub>OUT</sub> = 1.5A,<br>V <sub>IN</sub> = 1.8V, V <sub>OUT</sub> = 1.5V |     | 50                    |      | - dB              |

|                      |                                                                 | 300kHz, $I_{OUT} = 1.5A$ ,<br>$V_{IN} = 1.8V$ , $V_{OUT} = 1.5V$                  |     | 30                    |      |                   |

| Noise                | Output noise voltage                                            | 100Hz to 100kHz, $I_{OUT}$ = 3.0A, $C_{SS}$ = 0.001 $\mu$ F                       |     | 25 × V <sub>OUT</sub> |      | μV <sub>RMS</sub> |

| t <sub>STR</sub>     | Minimum startup time                                            | R <sub>LOAD</sub> for I <sub>OUT</sub> = 1.0A, C <sub>SS</sub> = open             |     | 200                   |      | μs                |

| I <sub>SS</sub>      | Soft-start charging current                                     | V <sub>SS</sub> = 0.4V                                                            |     | 440                   |      | nA                |

| V <sub>EN, HI</sub>  | Enable input high level                                         |                                                                                   | 1.1 |                       | 5.5  | V                 |

| V <sub>EN, LO</sub>  | Enable input low level                                          |                                                                                   | 0   |                       | 0.4  | V                 |

| V <sub>EN, HYS</sub> | Enable pin hysteresis                                           |                                                                                   |     | 50                    |      | m∨                |

| V <sub>EN, DG</sub>  | Enable pin deglitch time                                        |                                                                                   |     | 20                    |      | μs                |

| I <sub>EN</sub>      | Enable pin current                                              | V <sub>EN</sub> = 5V                                                              |     | 0.1                   | 1    | μA                |

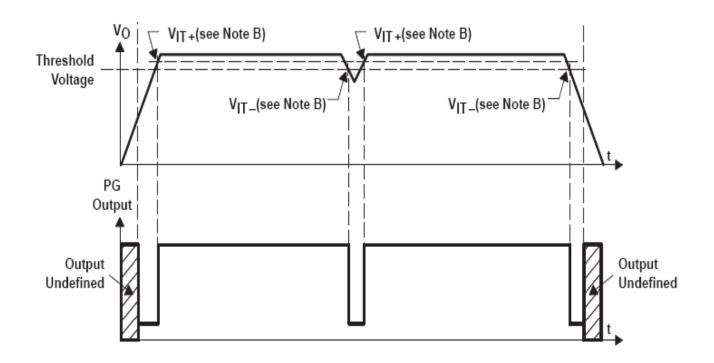

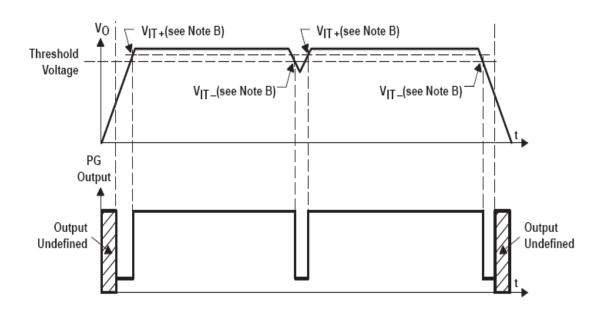

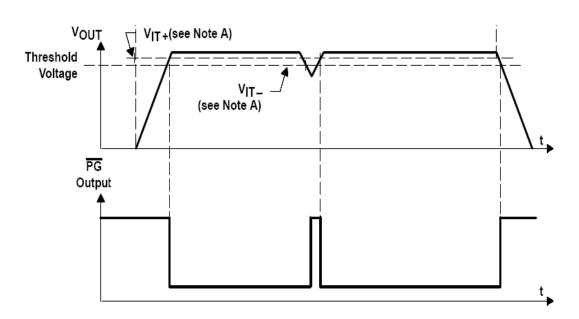

| V <sub>IT</sub>      | PG trip threshold                                               | V <sub>OUT</sub> decreasing                                                       | 85  | 90                    | 94   | %V <sub>OUT</sub> |

| V <sub>HYS</sub>     | PG trip hysteresis                                              |                                                                                   |     | 3                     |      | %V <sub>OUT</sub> |

| V <sub>PG, LO</sub>  | PG output low voltage                                           | I <sub>PG</sub> = 1mA (sinking), V <sub>OUT</sub> < V <sub>IT</sub>               |     |                       | 0.3  | V                 |

| I <sub>PG, LKG</sub> | PG leakage current                                              | $V_{PG}$ = 5.25V, $V_{OUT} > V_{IT}$                                              |     | 0.1                   | 1    | μA                |

| TJ                   | Operating junction temperature                                  |                                                                                   | -40 |                       | +125 | °C                |

| T <sub>SD</sub>      | Thermal shutdown temperature                                    | Shutdown, temperature increasing                                                  |     | +165                  |      | - °C              |

|                      |                                                                 | Reset, temperature decreasing                                                     |     | +140                  |      |                   |

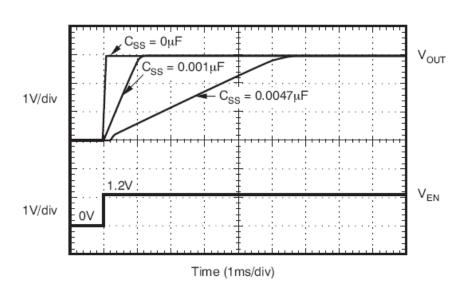

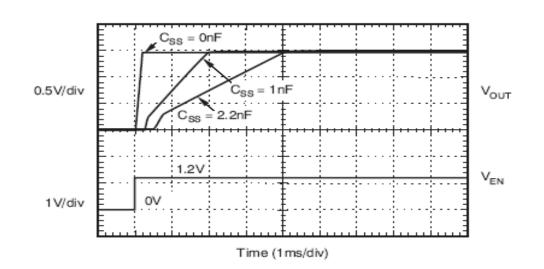

#### SOFT START PROGRAMMABILE (SS)

soft start time: Css defines a suitable value of start time when LDOs provide power supply to digital board (FPGA, DSP...) that need to be initialised.

$$t_{SS}(s) = 0.8 \times C_{SS}(F)/7.5 \times 10^{-7}$$

Table 2. Standard Capacitor Values for Programming the Soft-Start Time<sup>(1)</sup>

| C <sub>ss</sub> | SOFT-START TIME |

|-----------------|-----------------|

| Open            | 0.1ms           |

| 470pF           | 0.5ms           |

| 1000pF          | 1ms             |

| 4700pF          | 5ms             |

| 0.01µF          | 10ms            |

| 0.015µF         | 16ms            |

# Vout setting with feedback resistor R1 and R2

Table 1. Standard 1% Resistor Values for Programming the Output Voltage<sup>(1)</sup>

| R <sub>1</sub> (kΩ) | R <sub>2</sub> (kΩ) | V <sub>OUT</sub> (V) |

|---------------------|---------------------|----------------------|

| Short               | Open                | 0.8                  |

| 0.619               | 4.99                | 0.9                  |

| 1.13                | 4.53                | 1.0                  |

| 1.37                | 4.42                | 1.05                 |

| 1.87                | 4.99                | 1.1                  |

| 2.49                | 4.99                | 1.2                  |

| 4.12                | 4.75                | 1.5                  |

| 3.57                | 2.87                | 1.8                  |

| 3.57                | 1.69                | 2.5                  |

| 3.57                | 1.15                | 3.3                  |

Per avere la maggiore accuratezza possibile R2 dovrebbe essere ≤ 4.99kΩ

$$V_{OUT} = 0.8 \times (1 + R_1/R_2)$$

# CIN, CBIAS, COUT

- $C_{OUT} \ge 2.2 \mu F$

- $C_{IN}$  and  $C_{BIAS} \ge 1 \mu F$ . If Vin and Vbias are connected to the same voltage source  $C_{BIAS} \ge 4.7 \mu F$

- Ceramic capacitors with low ESR need to be mounted as close as possible to device pins.

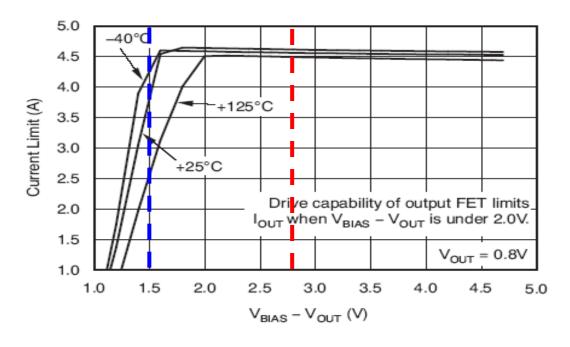

## **Output Current limitation**

Case 1

$$\begin{cases} V_{BIAS}=4V \\ V_{OUT}=1.2V \\ V_{BIAS}-V_{OUT}=2.8V \end{cases}$$

Case 2

$$\begin{cases} V_{BIAS}=4V \\ V_{OUT}=2.5V \\ V_{BIAS}-V_{OUT}=1.5V \end{cases}$$

Note: with low  $(V_{BIAS} - V_{OUT})$  the current limit is temperature dependent!

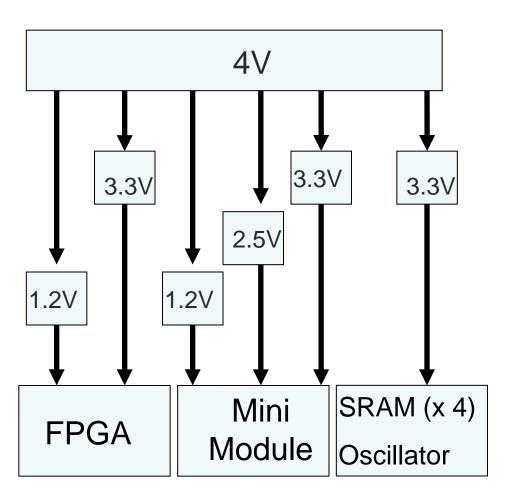

# Example of Power Supply for a digital board (Prima project)

- Primary voltage source is chosen +4V from a switching regulator and different outputs for the digital components are provided.

- The board host high sensitivity sensors for radiation detection: low noise power supply is required LDO

#### Power supply specifications

| DISPOSITIVO | CORRENTE<br>STAND BY | CORRENTE<br>ATTIVA |  |

|-------------|----------------------|--------------------|--|

| FPGA        | 175mA                | 3.6A               |  |

| MiniModule  | 445mA                | 6A                 |  |

| Memoria     | 200mA                | 1.1A               |  |

| Oscillatore | Sempre attivo        | 40mA               |  |

Load currents

**POTENZA** POTENZA (max) DISSIPATA DISSIPATA **DISPOSITIVO** STAND BY **ATTIVA FPGA** 0.53W8.73W MiniModule 1.07W 14W Memoria 0.66W3.63W Oscillatore Sempre attivo 0.132W

Power dissipation

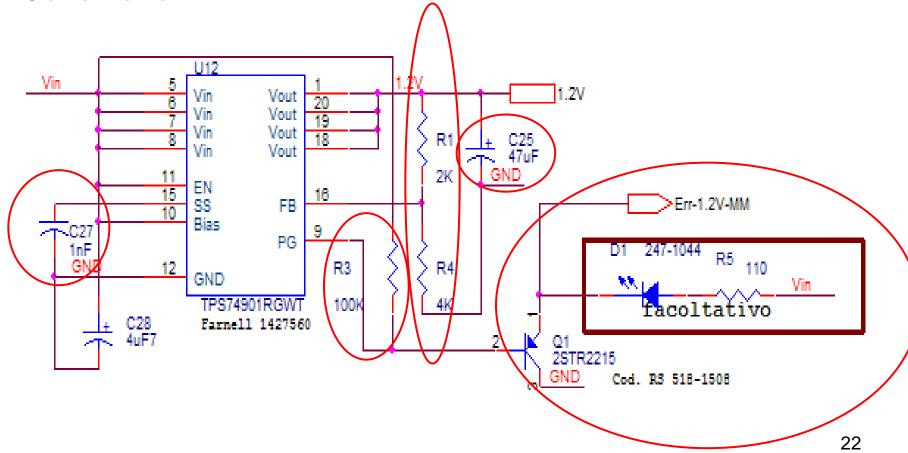

#### LDO Vout=1.2V TPS74901RGWT

- Reference voltage 1.2V set by external feed back resistors

- Max Output current 3A

- EN enable pin handled

RGW Package QFN-20 (top view)

- SS "soft start", Css = 1nF to delay of about 2 ms

#### LDO Vout=1.2V TPS74901RGWT

- PG Vout monitoring, goes to low impedance if an error is detected on output voltage regulation. Power diagnostic firmware handles this pin output.

#### LDO Vout=1.2V TPS74901RGWT

#### Schematic.

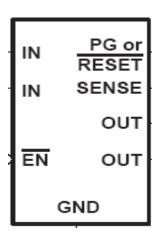

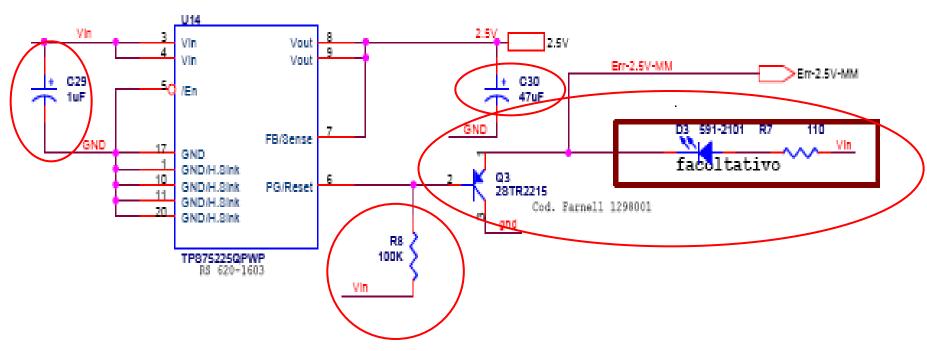

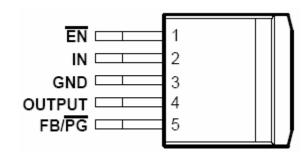

#### LDO Vout = 2.5V TPS75225QPWP

- Output voltage 2.5V

- Max Output Current 2A

- Package TSSOP (QPWP) 20 pin

- PG output handled

- /EN pin

#### LDO Vout = 2.5V TPS75225QPWP

#### Schematic.

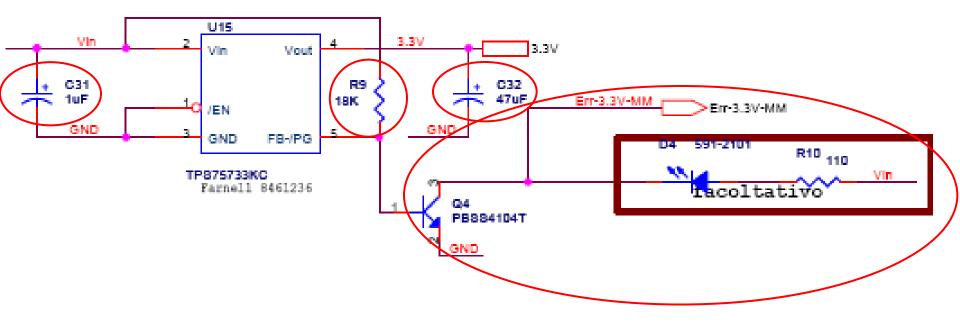

#### LDO Vout = 3.3V TPS75733KC

- Output voltage 3.3V

- Current output 3A

- Package TO-263 KTT

- PG handled

- -/EN

#### LDO Vout= 3.3V TPS75733KC

#### Schematic.

Cout suggested 47uF with ESR  $< = 200 \text{m}\Omega$ .

Cin ceramic (0.22 – 1)uF

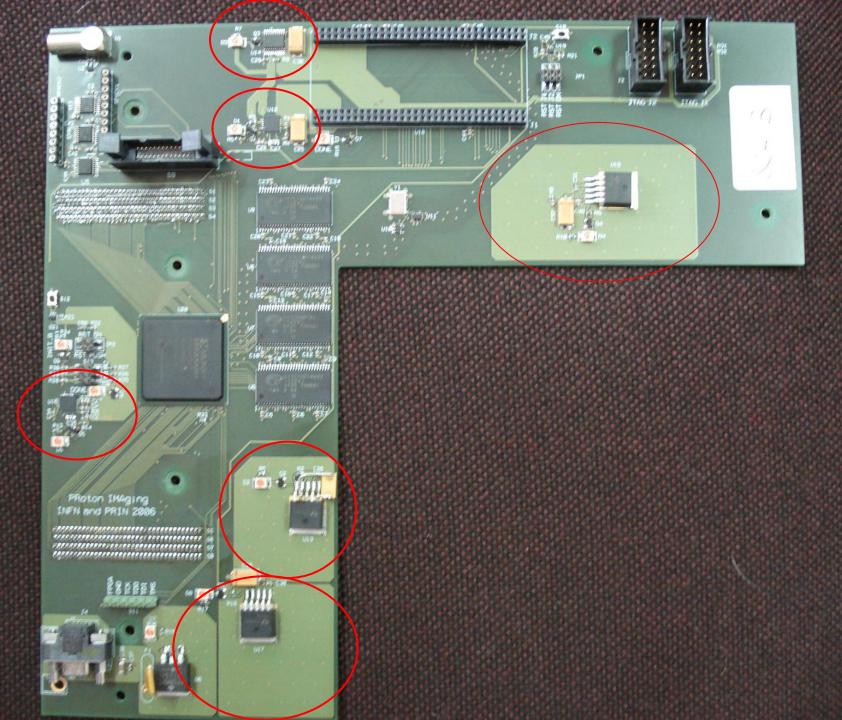

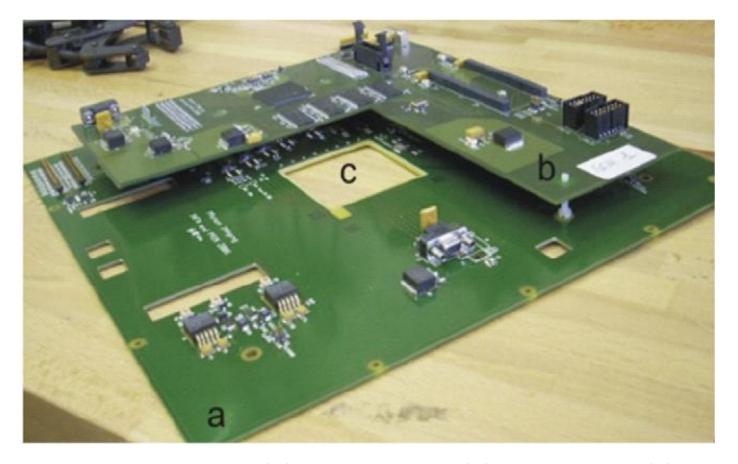

#### FINAL BOARD

Front-end board (a); digital board (b); sensor slot (c).